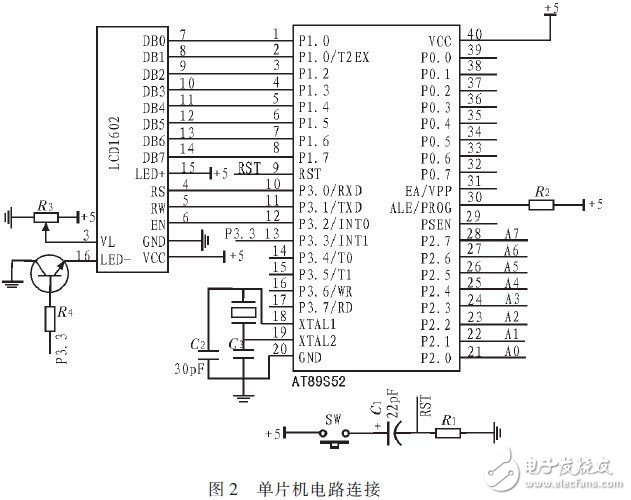

单片机应用系统工作时,除了进入系统正常的初始化之外,当由于程序运行出错或操作错误使系统处于死锁状态时,为摆脱困境,也需按复位键以重新启动。所以系统的复位电路必须准确、可靠地工作。单片机的复位都是靠外部电路实现的,在时钟电路工作后,只要在单片机的RST引脚上出现24个时钟振荡脉冲(即2个机器周期)以上的高电平,单片机便实现初始化状态复位。为了保证应用系统可靠地复位,系统采用按键电平复位方式。

单片机AT89S52的P1口与液晶显示模块LCD1602的数据端口相连,P3.2控制液晶模块的读写;对比度调整端连接一个10 kΩ的可调电阻,用来调整液晶显示亮度。另外,单片机的P2口与CPLD的8个I/O口相连,以进行数据传输,其电路设计如图2所示。

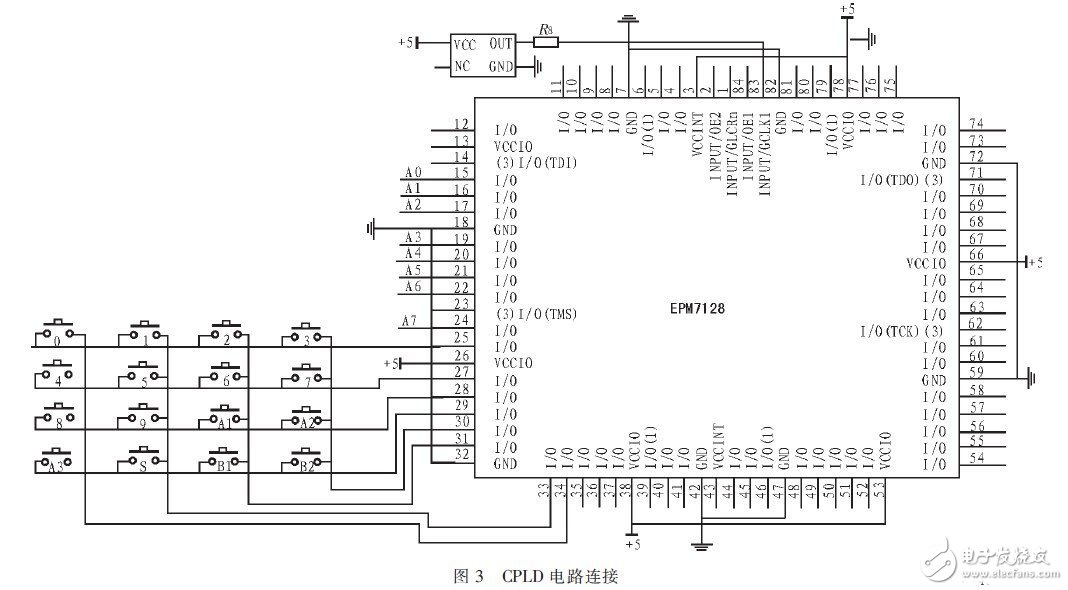

CPLD电路设计

晶振是为处理器提供频率基准的元器件,属于系统不可或缺的一部分。通常分为有源晶振和无源晶振两个大类,无源晶振要求芯片内部有震荡器,并且其信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确的匹配外围电路,如需更换晶振要同时更换外围电路。有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。

EPM7128SLC84需要提供外部时钟信号,由于CPLD对时钟精度要求甚高,通过前面的分析可知有源晶振的通信质量和精度较无源晶振高,所以采用1.000 MHz的有源晶体振荡器,电路的输出端口与处理器EPM7128SLC84的GCKL1连接,其具体电路设计如图3所示。

。 (本文来源网友上传,如有侵权,可联系管理员删除)

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时联络我们,采取适当措施,避免给双方造成不必要的经济损失。