1 引言

随着存储技术的不断进步,Flash Memory的存储容量越来越大,读写数度越来越快。性能价格比越来越高。但是,NAND Flash本身存在缺点,归纳起来有两点:读写控制时序复杂和位交换(o、1反转)问题。NAND Flash器件能够复用指令、地址和数据总线,从而节省了引脚数量,但引脚不仅承担着数据总线的功能,还承担着地址及指令总线的功能,所以造成接口控制时序复杂。位反转的问题更多见于NAND Flash,NAND Flash的供应商建议使用NAND Flash的同时使用EDC/ECC校验算法。

本文实现的NAND Flash控制器放置在CPU和NANF Flash器件之间,实现了NAND Flash的无粘接接口,可以大大简化CPU对NAND Flash的操作时序,提高CPU的使用效率。ECC功能可以保证存储数据的准确性,ECC模块和主控模块相对独立,在不需要ECC功能的时候,只需不使能ECC模块,方便灵活。

2 控制接口电路的功能特性

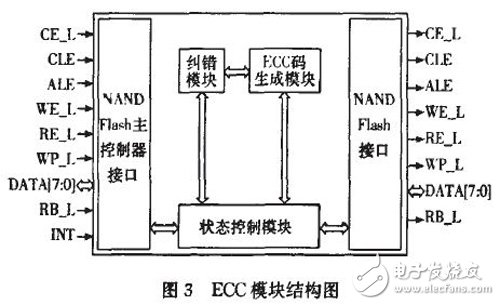

整个控制接121电路分为两大功能模块:第一个功能模块为主控制器模块,该模块简化NAND Flash的接口时序,可以为NAND Flash设计一个无粘接接口(Glueless Inter一face),从而使得对NAND Flash操作的时序复杂程度大大降低,使得NAND Flash接口映射为一个类似于SRAM的无粘结接口。第二个功能模块是ECC模块,该模块对512个字节能纠正单比特错误和检测双比特错误,但对单比特以上的错误无法纠正。对两比特以E的错误不保证能检测。

两个功能模块相对独立,ECC功能模块位于主控制器模块与NAND Flash芯片之间,可以选择工作与不工作,主控制器模块的所有命令都会通过ECC模块传给NANDFlash芯片。当令ECC模块不工作时。ECC模块就相当于连接主控制器模块与NAND Flash芯片的导线;当ECC模块工作时。只会在丰控制器模块的操作中加入一些步骤,并不会打乱主控制器模块的操作时序。

3 主控制器

3.1寄存器和缓存配置

主控制器的外部接口类似于SRAM的,然而SRAM只有读和写两种主要操作。而NAND Flash除r页编程与读操作之外还有ID读取、重置、块擦除和状态读取等操作,在不改变接口的情况下只能采用与NAND Flash类似的写控制字的方式。主控制器有16字节寄存器组,可以从I/O总线上读取指令和地址。指令寄存器采用存储器映射(Memory Mapped Register)的编址方式,也就是说,寄存器的地址统一编入内存空间,从0xFF0到OxFFA。

3.2主控制器的实现

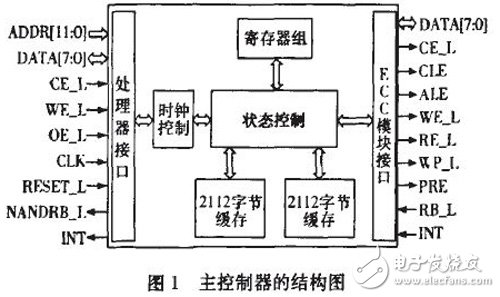

主控制器的结构框图见图1。下面分别讨论时钟控制模块和状态控制模块的设计实现。

基于FPGA的控制接口电路设计

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时联络我们,采取适当措施,避免给双方造成不必要的经济损失。