ECL 电路简介

ECL电路(即发射极耦合逻辑电路Emitter-Couple Logic)是一种非饱和型的数字逻辑电路,电路内晶体管工作在线性区或截止区,速度不受少数载流子的存储时间的限制,所以它是现有各种逻辑电路中速度最快的一种, 能满足高达10Gbps工作速率。最先由Motorola公司提出ECL标准。ECL 的主要分类如下。

| PECL | VCC=5.0V,VEE=0.0V |

| LVPECL | VCC =3.3V,VEE =0.0V VCC =2.5V,VEE =0.0V |

| NECL | VCC =0.0V,VEE =-5.2V |

| LVNECL | VCC=0.0V,VEE =-3.3V VCC =0.0V,VEE =-2.5V |

PECL即Positive Emitter-Couple Logic,也就是正发射极耦合逻辑的意思,使用5.0V电源。PECL 是由ECL 演变而来的,ECL 即Emitter-Couple Logic,也就是发射极耦合逻辑。ECL 有两个供电电压VCC和VEE。当VEE接地时,VCC 接正电压时,这时的逻辑称为PECL;当VCC 接地时,VEE接负电压时,这时的逻辑成为NECL,VEE一般接-5.2V电源;一般狭义的ECL 就是指NECL。由于PECL/LVPECL可以和系统内其他电路共用一个正电源供电,所以PECL/ LVPECL相对于ECL应用更为广泛。起初的PECL器件是将VCC接+5V,后来为了直接利用广泛使用的3.3V和2.5V电压,出现了VCC=3.3V/2.5V的LVPECL(Low Voltage PECL)。

PECL/LVPECL电路结构

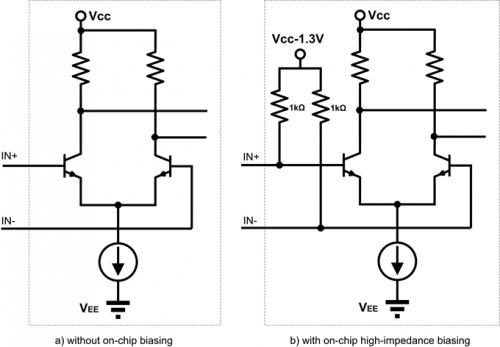

PECL 的输入是一个具有高输入阻抗的差分对,该差分对的共模电压需要偏置到VBB =VCC-1.3V,这样允许的输入信号电平动态最大。对于不同芯片的输入级,信号允许的共模电平可能会有些差异,请参考相应的datasheet。有部分芯片在内部已经集成了偏置电路,使用时直接连接即可,有的芯片没有加,使用时需要在芯片外部加直流偏置。

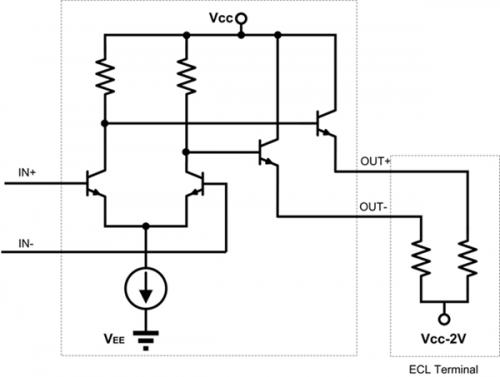

PECL的标准输出负载是串联50ohm至VCC-2V的电平上,在这种负载条件下,OUT+与OUT-的共模电压是VBB=VCC-1.3V,OUT+/OUT-的输出的平均电流为14mA。

。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时联络我们,采取适当措施,避免给双方造成不必要的经济损失。