JTAG(Joint Test AcTIon Group,联合测试行动组)是一种国际标准测试协议(IEEE 1149.1兼容)。标准的JTAG接口是4线——TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 JTAG是最基本的通讯协议之一,大家可以理解为与RX TX或者USB的道理是一样的,只是一种通讯手段,但与RX TX以及USB有很重大的不同,那就是这个JTAG协议是最底层的,说的通俗一点,一般来说,手机里边,CPU是老大,对吧?但在JTAG面前,他就不是老大了,JTAG协议就是用来控制CPU的,在JTAG面前CPU变成喽啰了。一般的协议是求着CPU读写字库的程序,但JTAG可以读写CPU的程序,命令让CPU啥活都干,擒贼先擒王,JTAG就是屠龙刀。

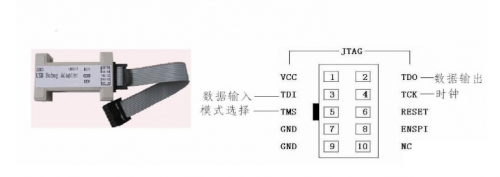

JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出;TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;TRST为测试复位,输入引脚,低电平有效 JTAG的主要功能有两种,或者说JTAG主要有两大类:一类用于测试芯片的电气特性,检测芯片是否有问题;另一类用于Debug,对各类芯片以及 其外围设备进行调试。一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器、挂在CPU总线上的设备以及内置模块的寄存器。本文主要介绍 的是Debug功能。 注释:JTAG可以访问一些内部寄存器,主要是CPU内的寄存器,例如一些通用寄存器等;也可以访问一些挂在总线上的设备,比如片内的内存L1,L2,L3等;还可以访问内置模块的寄存器,比如MMU模块,通过JTAG都可以访问这些寄存器。

1 JTAG原理分析 简单地说,JTAG的工作原理可以归结为:在器件内部定义一个TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试和调试。首先介绍一下边界扫描和TAP的基本概念和内容。

1.1 边界扫描 边界扫描(Boundary-Scan)技术的基本思想是在靠近芯片的输入/输出引脚上增加一个移位寄存器单元,也就是边界扫描寄存器(Boundary-Scan Register)。 当芯片处于调试状态时,边界扫描寄存器可以将芯片和外围的输入/输出隔离开来。通过边界扫描寄存器单元,可以实现对芯片输入/输出信号的观察和控 制。对于芯片的输入引脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该引脚中去;对于芯片的输出引脚,也可以通过与之相连的边界扫描寄存 器“捕获”该引脚上的输出信号。在正常的运行状态下,边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一 种便捷的方式用于观测和控制所需调试的芯片。另外,芯片输入/输出引脚上的边界扫描(移位)寄存器单元可以相互连接起来,任芯片的周围形成一个边界扫描链 (Boundary-Scan Chain)。边界扫描链可以串行地输入和输出,通过相应的时钟信号和控制信号,就可以方便地观察和控制处在调试状态下的芯片。

1.2 测试访问口TAP TAP(Test Access Port)是一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。对整个TAP的控制是通过TAP控制器(TAP Controller)来完成的。下面先分别介绍一下TAP的几个接口信号及其作用。其中,前4个信号在IEEE1149.1标准里是强制要求的。 ◇TCK:时钟信号,为TAP的操作提供了一个独立的、基本的时钟信号。 ◇TMS:模式选择信号,用于控制TAP状态机的转换。 ◇TDI:数据输入信号。 ◇TDO:数据输出信号。 ◇TRST:复位信号,可以用来对TAP Controller进行复位(初始化)。这个信号接口在IEEE 1149.1标准里并不是强制要求的,因为通过TMS也可以对TAP Controller进行复位。

◇STCK:时钟返回信号,在IEEE 1149.1标准里非强制要求。 ◇DBGRQ:目标板上工作状态的控制信号。在IEEE 1149.1标准里没有要求,只是在个别目标板(例如STR710)中会有。 简单地说,PC机对目标板的调试就是通过TAP接口完成对相关数据寄存器(DR)和指令寄存器(IR)的访问。 系统上电后,TAP Controller首先进入Test-LogicReset状态,然后依次进入Run-Test/Idle、Select-DR- Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR状态,最后回到Run- Test/Idle状态。在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的。其中,在 Capture-IR状态下,一个特定的逻辑序列被加载到指令寄存器中;在Shift-IR状态下,可以将一条特定的指令送到指令寄存器中;在 Update-IR状态下,刚才输入到指令寄存器中的指令将用来更新指令寄存器。最后,系统又回到Run-Test/Idle状态,指令生效,完成对指令 寄存器的访问。当系统又返回到Run-Test/Idle状态后,根据前面指令寄存器的内容选定所需要的数据寄存器,开始执行对数据寄存器的工作。其基本 原理与指令其存器的访问完全相同,依次为Select-DR-Scan、Capture-DR、Shift-D、Exit1-DR、Update-DR, 最后回到Run-Test/Idle状态。通过TDI和TDO,就可以将新的数据加载到数据寄存器中。经过一个周期后,就可以捕获数据寄存器中的数据,完 成对与数据寄存器的每个寄存器单元相连的芯片引脚的数据更新,也完成了对数据寄存器的访问。 目前,市场上的JTAG接口有14引脚和20引脚两种。其中,以20引脚为主流标准,但也有少数的目标板采用14引脚。经过简单的信号转换后,可以将它们通用。

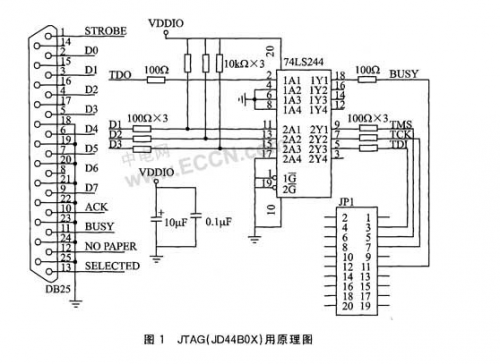

JTAG的基本原理进行分析 下面通过对JD44B0X实验开发板的简易JTAG的基本原理进行分析,以及对JD44B0X和STR710试验开发板主板的JTAG原理进行对比,进一步阐述JTAG的工作原理。JD44B0X实验开发板的简易JTAG的原理图如图1所示。

图1中,74LS244为三态输出的8组缓冲器和总线驱动器,其功能如表1所列。

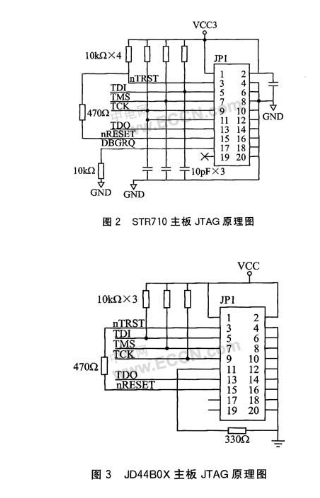

由表1可知,在JD44B0X实验板的调试过程中,这款简易JTAG的主要作用就是将PC机发出的电信号与实验板的电信号进行匹配,以实现驱动目标板的功能。 STR710和JD44B0X主板的JTAG原理图如图2和图3所示。

通过图2和图3的对比可以发现,虽然所用的仿真器有很大的差别,但是,实际上忽略一些上下拉电阻以及保护电容(这些电阻、电容对于电路功能没有意 义),它们的基本原理图是十分相似的,唯一的差别就在于对RTCK信号(用于测试时钟返回)和DBGRQ信号(用于设置目标板工作状态)的处理。实际上, 在IEEE 1149.1标准中这两个信号都不是强制要求的。因此,在分析仿真器(JTAG)的工作原理时完全可以忽略这两个信号的情况,而仅对IEEE 1149.1标准中强制要求的4个信号进行分析。

。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时联络我们,采取适当措施,避免给双方造成不必要的经济损失。