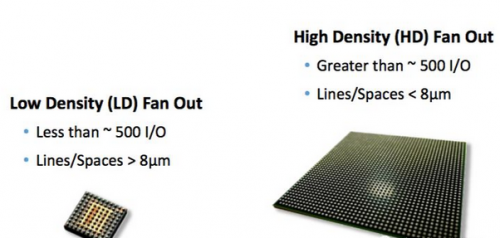

据我们了解,代工厂和OSAT正在开发更先进的fan-out,有些还在封装内部垂直堆叠裸片,一方面填补了低成本fan-out和封装系统之间的中间地带,另一方面也填补了2.5D和3D芯片之间的中间地带。 这些新的fan-out比以前的迭代产品具有更密集的互连,在某些情况下,它们包括多个布线层彼此堆叠在一起。台积电数月前已经拥有了这种堆叠技术,包括集成Fan-Out(InFo),现在,一些OSAT也正在采用自己的版本。 直到最近,fan-out几乎完全被视为低成本的高级封装选择,它基本上缩小了原本可以在PCB上找到的元件,并将所有元件都放在一个封装中。这种方法有许多优点。首先,把所有元件都放进小封装可以降低材料成本。其次,通过缩短信号传输距离,与更大的、完全集成的SoC相比,性能会提升,同时驱动这些信号所需要的电量也会下降。第三,通过将不同节点开发的芯片集成到同一器件中,芯片制造商可以优化布局规划,以减少诸如串扰、电源噪声和电迁移等物理效应。 这并不意味在低端fan-out的工作在减少。事实上,情况正好相反。新的EDA工具和流程正在开发和推出,面板级封装方法也适用于具有足够产量的器件。但高端fan-out将这种封装方式推向了一个新的方向,重点在于减少线路和空间以获得更高的密度,并显着提高性能。虽然大多数fan-out都有8μm以上的线路和空间,但是在新器件中可能会低至2μm。(线路和空间是金属轨迹的宽度和间距。)

图1:低密度fan-out vs高密度fan-out。 (来源:ASE/SEMI行业战略研讨会) Advanced Semiconductor Engineering(ASE)高级工程总监John Hunt表示:“大家都在考虑推出低端解决方案,但我们也将其视为高端解决方案。对于制造fan-out,你可以把一个芯片直接放在另一个芯片上。这对光子来说很好,因为大家希望它在50μm以内。你也可以使用fan-out作为裸片基板的替代品,因此你可以将芯片翻转到封装上。这样便可以让热量向下传递,跟向上传递一样。 ”

。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时联络我们,采取适当措施,避免给双方造成不必要的经济损失。